-

Data must be stable before and after the clock edge to be reliably transferred. If not properly synchrnozed there could be hazards (unexpected or undesired

signals), metastability - a condition caused by timing vioaltions and flip-flop outputs leading to erroneous data, race conditions bugs that come and go,

clock skew

-

Static hazards occur as the consequence of unequal delays in logic. One way to remove the hazard is to add another gate. The best way is to use flip-flops

with synchronous design!

-

-

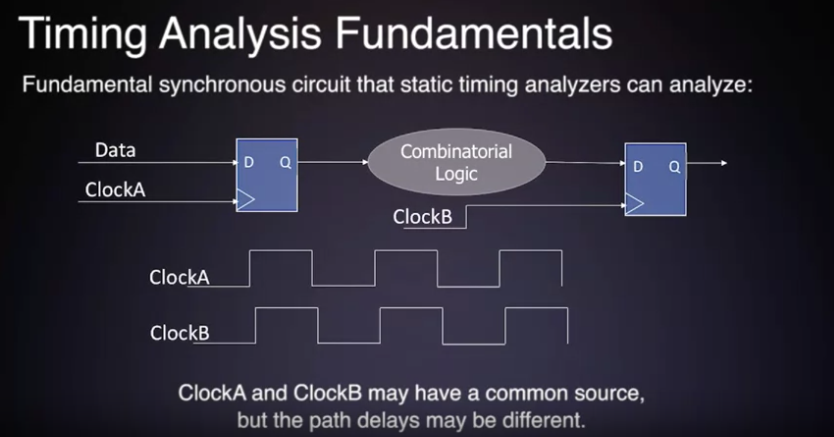

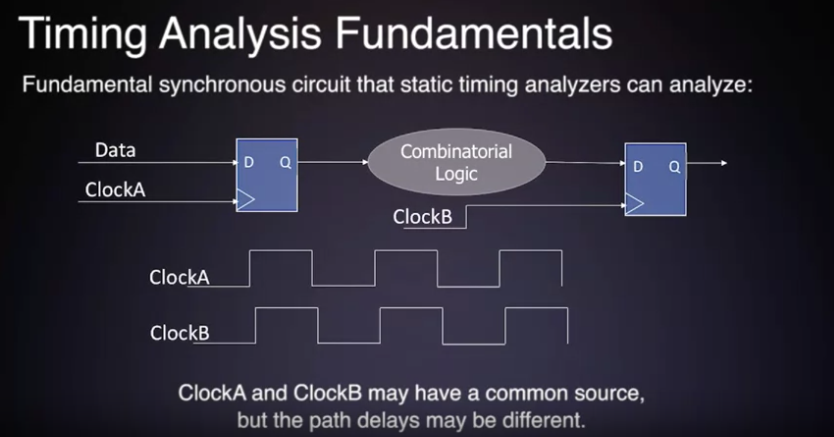

Clock A and Clock B may have the same source, but may have different delays.

-

Launch Edge = Clock Edge that activate sthe source register in a register-to-register path.

Latch Edge = Clock edge that activates the destination register and captures the data. Together they form a data requirement window.

-

Data Arrival Time = the time for data to arrive at a destination register's D input from the common clock edge.

Data (Setup) Arrival Time = Launch Edge + TclkA + Tco + Tdata

-

Clock Arrival Time = the time for clock to arrive at a destination register's clock input

-

Hold Time is defined as the minimum time the data signal must be stable after the clock edge

-

Data Required Time = the minimum time for the data to get latched into the destination register (AFTER the hold)

Data Required Time Hold = Clock Arrival Time + Th

Typical value is around 1 ns

-

Data Required Time (Setup) = the minimum time required for the data to get latched into the destination register (BEFORE the hold)

Data Required Time (Setup) = Clock Arrival time - Tsu (setup time usually specified in FPGA)

-

Setup slack = the margin by which the setup timing requirement is met

Setup Slack = Data Required Time (Setup) - Data Arrival Time

Setup Slack = Clock Period + TclkB - Tsu - TclkA - Tco - Tdata

-

Hold Slack = The margin by which the hold timing requirement is met

Hold Slack = Data Arrival Time - Data Required Time (Hold)

Hold Slack = TclkA + Tco + Tdata - TclkB - Th

-

When all timing is met, time enclosure is occuring. This is often a main goal of an FPGA's design.

-

I/O timing analysis uses the same slack equations.

-

Need to understand these to undersatnd cause of violation. Example causes, data path too long, requirements too short (incorrect analysis), large clock

skew signifying a gated clock etc

-

How to use timing quest analysis

-

Generate Timing netlist

-

Enter SDC constaints (Create and/or read in SDC file), constrain directly in console

-

Update timing netlist

-

Generate timing reports

-

Save timing constraints

-

User MUST enter constraints for all paths to fully analyze design. Timing analysis only performs slack analysis on constrained signals.

Constraints guide the fitter to place & route design in order to meet timing requirements. Prof recommends constraining all paths! (or at least clocks & I/O)